Tutorial 4: HBM System and Architecture for AI applications

Par un écrivain mystérieux

Last updated 20 juin 2024

Tutorial 4: HBM System and Architecture for AI applicationsSpeakers: Manish Jain and Nikhil Raghavendra Rao (Rambus)Tutorial Abstract: Artificial in

Memory Requirements for Embedded AI at the Edge

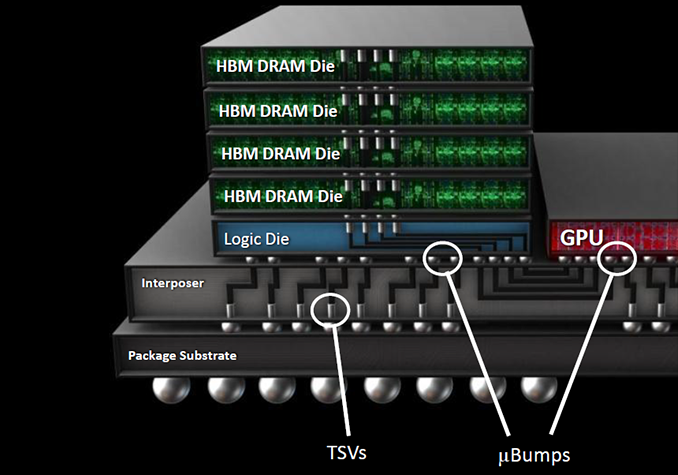

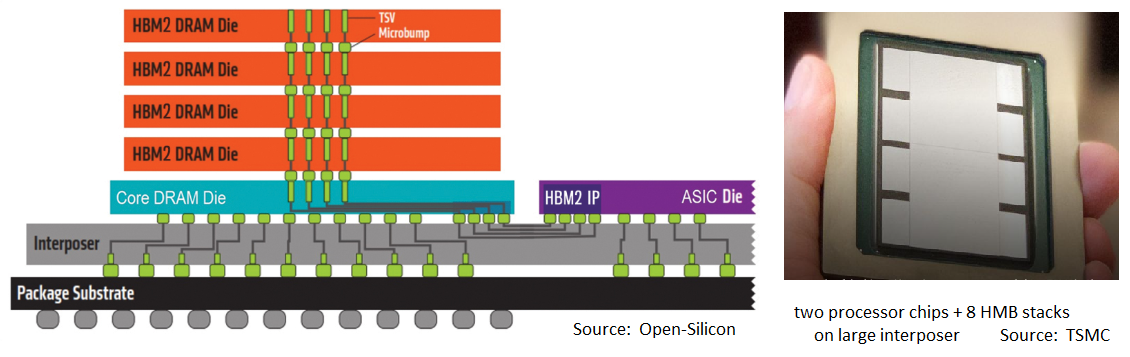

Simplified architectures of a multi-processor system where the memory

FPL'20: High Bandwidth Memory on FPGAs: A Data Analytics Perspective

AI Driving Renewed Interest in Processing-in-Memory - EE Times Asia

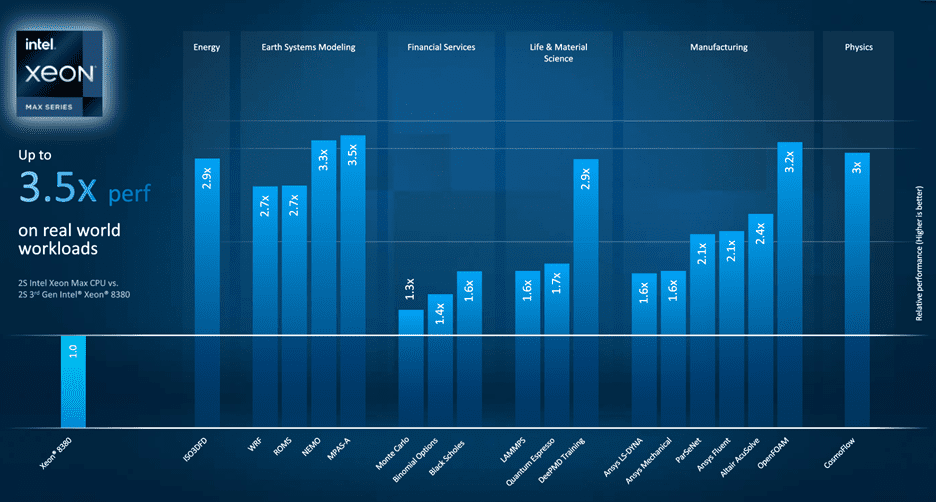

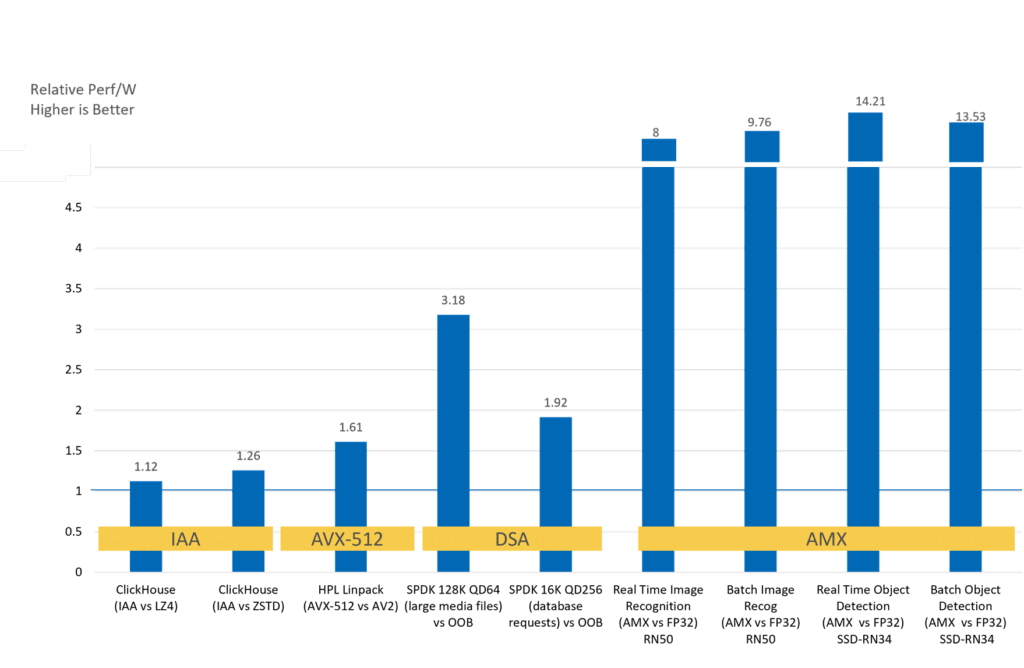

Internal CPU Accelerators and HBM Enable Faster and Smarter HPC and AI Applications

Micromachines, Free Full-Text

Processing-in-memory in High Bandwidth Memory Architecture with Efficient and Low Latency Channel

Basic Tutorial for Maximizing Memory Bandwidth with Vitis and Xilinx UltraScale+ HBM Devices

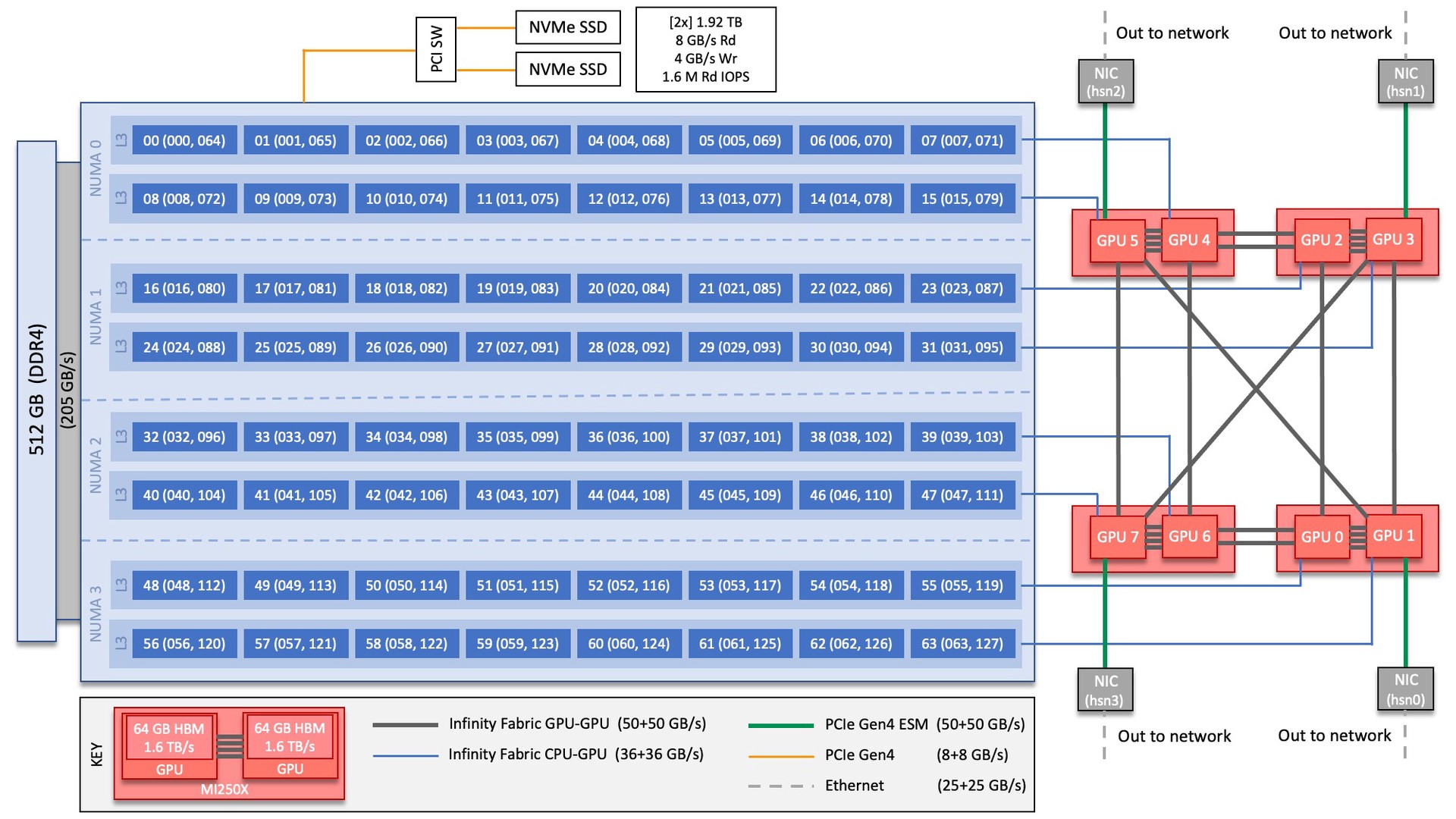

Frontier User Guide — OLCF User Documentation

Internal CPU Accelerators and HBM Enable Faster and Smarter HPC and AI Applications

Recommandé pour vous

HBM's Future: Necessary But Expensive14 Jul 2023

HBM's Future: Necessary But Expensive14 Jul 2023 JEDEC Publishes HBM2 Specification as Samsung Begins Mass14 Jul 2023

JEDEC Publishes HBM2 Specification as Samsung Begins Mass14 Jul 2023 Samsung going after SK hynix in AI memory chips - The Korea Times14 Jul 2023

Samsung going after SK hynix in AI memory chips - The Korea Times14 Jul 2023 AMD: We are actively promoting HBM and do not collect royalties14 Jul 2023

AMD: We are actively promoting HBM and do not collect royalties14 Jul 2023 HBM Architects and Interior Designers, Library Design14 Jul 2023

HBM Architects and Interior Designers, Library Design14 Jul 2023- High-bandwidth memory (HBM) options for demanding applications.14 Jul 2023

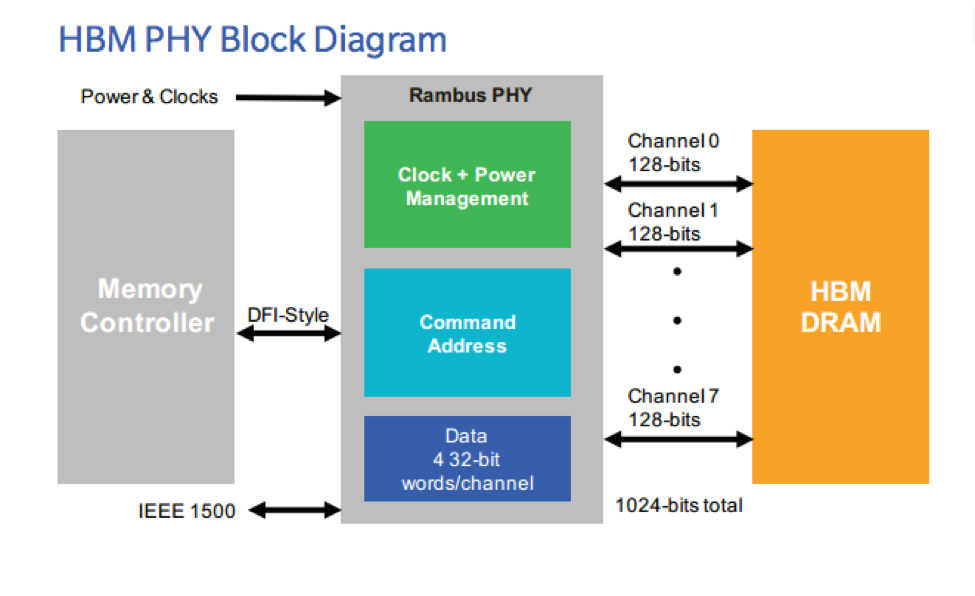

Taking a closer look at Rambus' HBM GEN2 PHY - The Next Platform14 Jul 2023

Taking a closer look at Rambus' HBM GEN2 PHY - The Next Platform14 Jul 2023- Global Hybrid Memory Cube (HMC) and High-bandwidth Memory (HBM14 Jul 2023

Thermo-compression bonding for Large Stacked HBM Die - SemiWiki14 Jul 2023

Thermo-compression bonding for Large Stacked HBM Die - SemiWiki14 Jul 2023 The Different ESD Events and their Models - HBM, CDM and MM14 Jul 2023

The Different ESD Events and their Models - HBM, CDM and MM14 Jul 2023

Tu pourrais aussi aimer

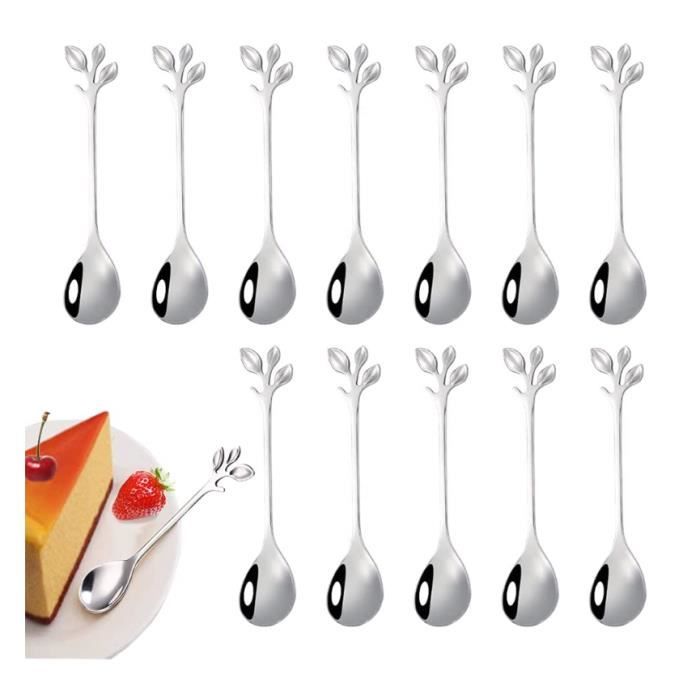

12 pièces de cuillère à café en feuille d'acier inoxydable, mini cuillère à café cuillère à dessert design branche, (Argent)14 Jul 2023

12 pièces de cuillère à café en feuille d'acier inoxydable, mini cuillère à café cuillère à dessert design branche, (Argent)14 Jul 2023 Roller fille - Roller en ligne réglable - Roller femme - Rollers Enfants - Roller lumineuse ajustable S(31-34 )M(35-38)L(39-42) - Achat / Vente Rollers en Ligne Enfant Adu - Cdiscount14 Jul 2023

Roller fille - Roller en ligne réglable - Roller femme - Rollers Enfants - Roller lumineuse ajustable S(31-34 )M(35-38)L(39-42) - Achat / Vente Rollers en Ligne Enfant Adu - Cdiscount14 Jul 2023 Comment choisir des bulbes de fleurs14 Jul 2023

Comment choisir des bulbes de fleurs14 Jul 2023 Pour la première fois, les physiciens ont fait interagir des14 Jul 2023

Pour la première fois, les physiciens ont fait interagir des14 Jul 2023 FILTRE A AIR POUR TETE DE COMPRESSEUR VF49514 Jul 2023

FILTRE A AIR POUR TETE DE COMPRESSEUR VF49514 Jul 2023 New Peugeot 5008 SUV – The SUV with 7 Modular Seats14 Jul 2023

New Peugeot 5008 SUV – The SUV with 7 Modular Seats14 Jul 2023 Support Canne à Pêche Porte Canne Rehausse - Kayak Sup Paddle14 Jul 2023

Support Canne à Pêche Porte Canne Rehausse - Kayak Sup Paddle14 Jul 2023 NEW BALANCE 574 Platform Sneaker14 Jul 2023

NEW BALANCE 574 Platform Sneaker14 Jul 2023 Lindy Adaptateur Displayport Vers Hdmi 4k (passif) à Prix Carrefour14 Jul 2023

Lindy Adaptateur Displayport Vers Hdmi 4k (passif) à Prix Carrefour14 Jul 2023 Pretty drap plat Tradilinge 100 % coton - Linge MAT14 Jul 2023

Pretty drap plat Tradilinge 100 % coton - Linge MAT14 Jul 2023